详解Xilinx Zynq UltraScale+ MPSoC产品PCB电路板设计

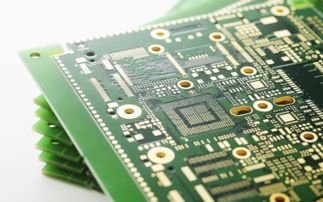

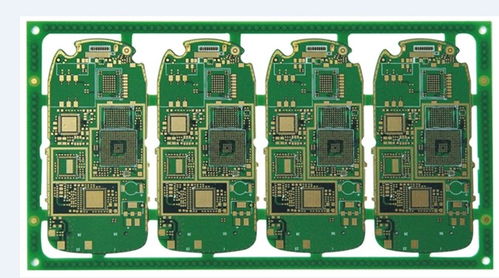

Xilinx的Zynq UltraScale+ MPSoC(多处理器片上系统)是业界领先的异构计算平台,集成了高性能ARM Cortex-A53/Cortex-R5应用与实时处理器、强大的可编程逻辑(FPGA)以及丰富的硬核IP。其PCB电路板设计是充分发挥该芯片潜力的关键环节,涉及高速信号完整性、电源完整性、热管理和机械结构等多个复杂领域。本文将深入解析其PCB设计的核心要点。

1. 芯片封装与焊球矩阵(BGA)

Zynq UltraScale+ MPSoC通常采用高密度球栅阵列封装,如FF(Fine-Pitch Fine Ball Grid Array)或RF(RF-Enhanced)系列。设计前,必须仔细研究芯片的封装手册,明确以下几点:

- 电源与地焊球分布:芯片拥有数十个独立的电源域(如VCCINT, VCCBRAM, VCCAUX, VCCO for banks, PS电源等)。PCB需提供低阻抗、低噪声的供电路径。

- 信号Bank分组:I/O Bank被划分为多个组,每个组有独立的VCCO电压参考。设计时需确保信号在其所属Bank的电压标准下工作。

- 高速收发器(GTY/GTM)位置:这些用于PCIe、SATA、以太网等高速接口的引脚对布局和布线有极其严格的要求。

2. 电源分配网络(PDN)设计

这是设计的重中之重。MPSoC对电源噪声极其敏感,不良的PDN会导致系统不稳定、性能下降甚至启动失败。

- 多电压域与排序:芯片要求多个电源按特定顺序上电/断电。必须使用电源管理IC(PMIC)或分立电源方案实现正确的时序控制。

- 电源层分割与叠层:建议采用至少8层以上的PCB,为关键电源(如VCCINT、VCCAUX)和地提供完整的平面。电源平面应合理分割,避免重叠,以减少噪声耦合。

- 去耦电容布局:遵循“就近原则”,将不同容值(如大容量钽电容、中容量陶瓷电容和小容量0402/0201电容)尽可能靠近芯片的相应电源焊球放置,以提供从低频到高频的全频段低阻抗路径。

3. 高速信号完整性(SI)设计

- DDR4/LPDDR4接口:MPSoC的PS(处理系统)部分支持高速DDR存储器。设计需遵循严格的长度匹配、拓扑结构(通常为点对点)、阻抗控制(通常单端40Ω,差分80Ω)以及等长要求。需进行前仿真以确定布线长度、过孔数量和终端匹配方案。

- 高速收发器(GTY)布线:这是PCB设计中最具挑战的部分。要求:

- 使用差分对布线,严格控制差分阻抗(通常85Ω或100Ω)。

- 极短的引线长度,尽可能减少过孔。

- 相邻通道间需保持足够的间距,并参考完整的地平面,以减小串扰。

- 收发器的电源(如MGTAVCC, MGTAVTT)需要极其“干净”的隔离。

- 普通I/O与时钟:对于PS和PL(可编程逻辑)端的其他高速信号(如千兆以太网、USB、SDIO等),也需做好阻抗控制和匹配。全局时钟网络应优先布线,并做好屏蔽。

4. 热设计

Zynq UltraScale+ MPSoC功耗可观,尤其在PL端全速运行时。

- 热分析:早期需使用功耗估算工具进行热仿真。

- 散热方案:根据封装类型(如是否带散热盖),设计可能需要散热片、热管甚至风扇。PCB上芯片底部应布置足够的热通孔阵列,将热量传导至底层或内部接地层散发。

- PCB材料:对于极高功耗应用,可考虑使用高热导率的PCB基材。

5. 设计流程与检查清单

- 前期准备:深入研究Xilinx官方文档,包括数据手册、PCB设计指南、电源设计指南和信号完整性应用笔记。

- 原理图设计:正确连接所有电源、配置引脚(如Boot Mode)、调试接口(如JTAG)和必要的上拉/下拉电阻。

- 布局规划:优先放置MPSoC芯片、DDR存储器、PMIC、高速连接器和时钟源。确保电源路径顺畅,高速信号路径短直。

- 布线实施:分层分区布线,优先处理高速收发器线和DDR线,然后是其他关键信号,最后是低速信号。

- 后期验证:进行设计规则检查(DRC)、电气规则检查(ERC),并建议使用SI/PI仿真工具进行后仿真验证。

- 制板与装配:选择工艺可靠的PCB制造商,强调对阻抗控制、层间对准和表面处理的要求。焊接推荐使用BGA返修台或专业的SMT生产线。

###

Zynq UltraScale+ MPSoC的PCB设计是一项系统工程,要求工程师具备跨领域的知识。成功的板卡是性能、功耗、成本和可靠性的最佳平衡。严格遵循Xilinx的设计指南,借助先进的EDA工具进行仿真与验证,是确保一次成功的关键。对于复杂设计,强烈建议参考Xilinx官方的评估板原理图和PCB布局,它们提供了经过验证的最佳实践范例。

最新产品

详解Xilinx Zynq UltraScale+ MPSoC产品PCB电路板设计

长宁区专业电子产品回收与销毁 聚焦PCB电路板的环保处置

遂宁厂家直销 CPSR定制真空海绵吸具传感器薄膜吸盘在PCB电路板搬运中的应用

信广告不如自己挑 主板布线做工用料全解析之PCB电路板

深圳市锦佳兴电子柔性线路板(FPC)与PCB电路板产品列表及技术应用

深圳市平泰电子科技 核心产品线全览——刚性线路板(PCB)

电子说 深度解析PCB电路板的设计与应用

腾创达线路板 卓越品质与创新技术引领PCB电路板行业

谁是DX11新卡皇?GTX590与四大顶级显卡的PCB电路板鏖战

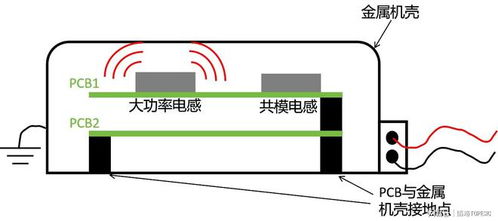

大功率DC电源整改中PCB接地设计的关键重要性